單片微波集成電路(MMIC)設(shè)計(jì)中的匹配網(wǎng)絡(luò) 原理、實(shí)現(xiàn)與挑戰(zhàn)

在單片微波集成電路(Monolithic Microwave Integrated Circuit, MMIC)的設(shè)計(jì)與制造過(guò)程中,匹配網(wǎng)絡(luò)(Matching Network)扮演著至關(guān)重要的角色。它不僅是連接不同功能模塊、確保信號(hào)高效傳輸?shù)臉蛄海菦Q定整個(gè)電路系統(tǒng)性能、如增益、噪聲系數(shù)、輸出功率和效率的關(guān)鍵因素。本文將深入探討MMIC匹配網(wǎng)絡(luò)的設(shè)計(jì)原理、常用實(shí)現(xiàn)方法以及面臨的技術(shù)挑戰(zhàn)。

一、匹配網(wǎng)絡(luò)的核心原理與目標(biāo)

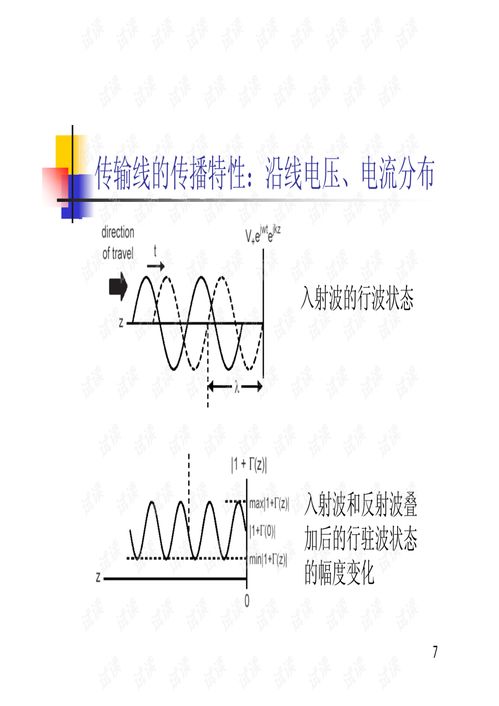

匹配網(wǎng)絡(luò)的核心目標(biāo),是實(shí)現(xiàn)信號(hào)源與負(fù)載之間、或各級(jí)電路之間的阻抗匹配,以最大化功率傳輸并最小化信號(hào)反射。在微波頻段,任何阻抗不連續(xù)都會(huì)導(dǎo)致信號(hào)反射,從而引起駐波、損耗增加、帶寬受限,甚至造成系統(tǒng)不穩(wěn)定。對(duì)于MMIC而言,由于所有元件(有源器件如晶體管,無(wú)源元件如電感、電容、傳輸線(xiàn))都集成在同一塊半導(dǎo)體襯底(通常是GaAs或GaN)上,其寄生參數(shù)效應(yīng)更為顯著,這使得精確的阻抗匹配變得尤為復(fù)雜和重要。

理想的匹配通常指將復(fù)數(shù)負(fù)載阻抗(ZL)變換為信號(hào)源阻抗(通常是標(biāo)準(zhǔn)的50歐姆)。匹配網(wǎng)絡(luò)通過(guò)引入電抗元件(電感L和電容C)或利用傳輸線(xiàn)的特性,在特定的工作頻率或頻帶內(nèi),抵消負(fù)載中的電抗部分,并使其實(shí)部等于源阻抗。

二、MMIC匹配網(wǎng)絡(luò)的常用實(shí)現(xiàn)方法

在MMIC設(shè)計(jì)中,匹配網(wǎng)絡(luò)的實(shí)現(xiàn)主要依賴(lài)于片上集成的無(wú)源元件和傳輸線(xiàn)結(jié)構(gòu)。

- 集總元件匹配網(wǎng)絡(luò):

- L型網(wǎng)絡(luò):是最基本的結(jié)構(gòu),由兩個(gè)電抗元件(一個(gè)串聯(lián)、一個(gè)并聯(lián))組成。結(jié)構(gòu)簡(jiǎn)單,但通常只能在單頻點(diǎn)實(shí)現(xiàn)完美匹配,帶寬較窄。

- π型和T型網(wǎng)絡(luò):由三個(gè)電抗元件構(gòu)成。相比L型網(wǎng)絡(luò),它們提供了更多的設(shè)計(jì)自由度,可以在匹配、帶寬和元件值可實(shí)現(xiàn)性之間進(jìn)行更好的折衷,常用于更復(fù)雜的匹配需求。

- 元件實(shí)現(xiàn):MMIC中的集總電感通常采用螺旋電感實(shí)現(xiàn),電容則采用金屬-絕緣層-金屬(MIM)結(jié)構(gòu)。設(shè)計(jì)時(shí)需精確考慮這些元件的寄生電阻、電容以及襯底損耗。

- 分布參數(shù)匹配網(wǎng)絡(luò):

- 利用微帶線(xiàn)、共面波導(dǎo)等傳輸線(xiàn)節(jié)來(lái)實(shí)現(xiàn)匹配。常見(jiàn)結(jié)構(gòu)包括四分之一波長(zhǎng)阻抗變換器、支節(jié)匹配器(單支節(jié)、雙支節(jié))等。

- 優(yōu)點(diǎn):在更高頻率(如毫米波頻段)下性能更優(yōu),功率處理能力通常更強(qiáng)。

- 缺點(diǎn):占用芯片面積較大,尤其是在低頻段。

- 混合匹配網(wǎng)絡(luò):

- 在實(shí)際MMIC設(shè)計(jì)中,常常結(jié)合使用集總元件和分布參數(shù)元件。例如,在較低頻率使用螺旋電感以節(jié)省面積,在關(guān)鍵的高頻路徑使用微帶線(xiàn)以保證性能。這種混合方式可以更靈活地優(yōu)化電路尺寸和性能。

三、MMIC匹配網(wǎng)絡(luò)設(shè)計(jì)的特殊考慮與挑戰(zhàn)

與分立元件或PCB級(jí)設(shè)計(jì)相比,MMIC匹配網(wǎng)絡(luò)設(shè)計(jì)面臨一系列獨(dú)特挑戰(zhàn):

- 模型精度:片上無(wú)源元件的精確電磁(EM)模型至關(guān)重要。設(shè)計(jì)師必須依賴(lài)精確的工藝設(shè)計(jì)套件(PDK)模型或進(jìn)行三維電磁場(chǎng)仿真,以捕捉元件間的寄生耦合和襯底效應(yīng)。

- 工藝偏差:半導(dǎo)體制造工藝存在不可避免的偏差,如介電層厚度、金屬線(xiàn)寬的變化。這會(huì)導(dǎo)致實(shí)際生產(chǎn)的MMIC其元件值與設(shè)計(jì)值存在差異,從而影響匹配性能。穩(wěn)健性設(shè)計(jì)(如寬頻帶匹配)和蒙特卡洛分析是應(yīng)對(duì)此挑戰(zhàn)的常用手段。

- 面積與成本:芯片面積直接關(guān)系到制造成本。匹配網(wǎng)絡(luò),尤其是分布參數(shù)網(wǎng)絡(luò),可能占用大量面積。設(shè)計(jì)師必須在性能與成本之間進(jìn)行精細(xì)權(quán)衡。

- 熱效應(yīng)與非線(xiàn)性:對(duì)于功率放大器等電路,大信號(hào)工作下器件參數(shù)會(huì)發(fā)生變化,且芯片溫度升高會(huì)影響元件特性。匹配網(wǎng)絡(luò)設(shè)計(jì)需考慮這種動(dòng)態(tài)變化,確保在大信號(hào)條件下仍能保持良好的性能。

- 多級(jí)間的相互影響:在多級(jí)放大器中,各級(jí)之間的匹配網(wǎng)絡(luò)并非獨(dú)立。輸出級(jí)的匹配會(huì)影響前級(jí)的負(fù)載牽引效應(yīng),需要進(jìn)行協(xié)同設(shè)計(jì)和整體優(yōu)化。

四、設(shè)計(jì)流程與工具

現(xiàn)代MMIC匹配網(wǎng)絡(luò)設(shè)計(jì)高度依賴(lài)于電子設(shè)計(jì)自動(dòng)化(EDA)工具。典型流程包括:

- 系統(tǒng)指標(biāo)確定:根據(jù)應(yīng)用(如低噪聲放大器、功率放大器、混頻器)確定增益、帶寬、噪聲、功率等核心指標(biāo)。

- 有源器件選擇與偏置:選擇合適的晶體管并確定其直流工作點(diǎn),在史密斯圓圖上標(biāo)出其小信號(hào)S參數(shù)或大信號(hào)阻抗。

- 拓?fù)溥x擇與初步設(shè)計(jì):根據(jù)帶寬和復(fù)雜度要求,選擇匹配網(wǎng)絡(luò)拓?fù)洌ㄈ鏛型、π型),利用史密斯圓圖或軟件工具進(jìn)行初步的阻抗變換計(jì)算。

- 電路仿真與優(yōu)化:將初步網(wǎng)絡(luò)代入完整的電路原理圖中,利用諧波平衡、SPICE等方法進(jìn)行線(xiàn)性/非線(xiàn)性仿真,并結(jié)合優(yōu)化算法對(duì)元件值進(jìn)行迭代優(yōu)化,以滿(mǎn)足所有性能指標(biāo)。

- 電磁協(xié)同仿真:對(duì)關(guān)鍵匹配網(wǎng)絡(luò)部分或整體版圖進(jìn)行2.5D或3D全波電磁仿真,以驗(yàn)證并修正寄生效應(yīng)的影響。

- 容差與良率分析:進(jìn)行蒙特卡洛分析,評(píng)估工藝偏差下的性能變化,確保設(shè)計(jì)的可制造性和良率。

結(jié)論

匹配網(wǎng)絡(luò)是MMIC設(shè)計(jì)的精髓所在,它深刻體現(xiàn)了微波理論與半導(dǎo)體工藝的結(jié)合。一個(gè)優(yōu)秀的匹配網(wǎng)絡(luò)設(shè)計(jì),不僅需要深厚的微波工程知識(shí),還需要對(duì)工藝細(xì)節(jié)的深刻理解以及對(duì)EDA工具的熟練運(yùn)用。隨著5G/6G通信、衛(wèi)星互聯(lián)網(wǎng)、雷達(dá)系統(tǒng)等應(yīng)用向更高頻段、更寬帶寬和更高集成度發(fā)展,MMIC匹配網(wǎng)絡(luò)的設(shè)計(jì)將繼續(xù)朝著寬帶化、小型化、高效率和可重構(gòu)性的方向演進(jìn),其復(fù)雜性和重要性也將與日俱增。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.colourstone.cn/product/44.html

更新時(shí)間:2026-04-08 21:57:45